連載

西川善司連載 / 「ATI Radeon HD 5800」徹底分析(3)〜3Dグラフィックスに特化したAMD

AMDの新世代GPU,「ATI Radeon HD 5800」(以下,HD 5800)の正体を,最上位モデル「ATI Radeon HD 5870」(以下,HD 5870)の分析を通じて明らかにしていく記事も最終回となった。今回は,第2回で始めたアーキテクチャ解説の続きから始めよう。

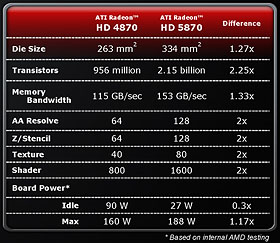

さてHD 5870では,SIMD Engineが「ATI Radeon HD 4870」(以下,HD 4870)の10基から20基へと2倍に強化された関係で,テクスチャユニットの総数も従来比2倍の20基となった。

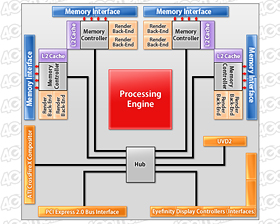

HD 5870のブロックダイアグラムから,SIMD Engine以降を抜き出したもの

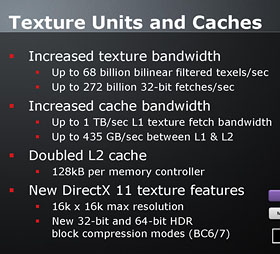

結論めいたものから先に述べると,テクスチャユニットそのもののアーキテクチャはHD 4800シリーズから変わっていないので,ほぼ同一と捉えていい。ただし,

- 最大テクスチャ解像度を16384×16384テクセルまで引き上げ

- 32bitおよび64bitのHDRテクスチャ圧縮(BC6Hモード)への対応

- 高品位LDRテクスチャ圧縮(BC7モード)への対応

といったDirectX 11(厳密にはDirect3D 11,以下同)新フィーチャーへの対応は盛り込まれている。

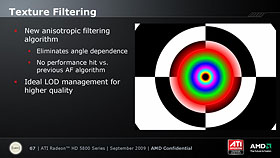

また,HD 5800シリーズのテクスチャフィルタリング処理では,“パフォーマンス向上のための姑息な最適化”をやめたことが宣言された。

高品位なテクスチャフィルタリング処理メソッドの一つに,異方性フィルタリングがあるが,これはかなり重い処理系だ。そこで,GPUメーカーの間では,見た目に分からない範囲で,視線との相対角度,あるいは視点からの距離などに応じて,テクスチャを階層縮小化した仕組み「MIPMAP」(ミップマップ)の参照法を切り換える,「最適化」という名の“手抜き”が行われていた。

具体的には,特定条件下でテクセルサンプル数を減らしたり,バイリニアフィルタリングに代行させたりしていたのだが,HD 5800シリーズでは,もう,そういう小手先のインチキはやめた,というわけである。

「そういった手抜きをせずとも,HD 5800シリーズは十分高速に処理できるようになったからだ」(第2回でも登場したAMDのDemers氏)。

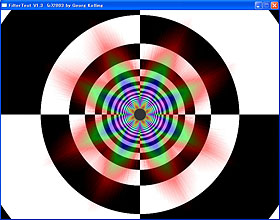

その証拠としてAMDは,HD 5800シリーズにおける異方性フィルタリングの適用結果がまったくの“インチキなし”であることを証明する,右のスライドを示している。

少し解説が必要だろう。

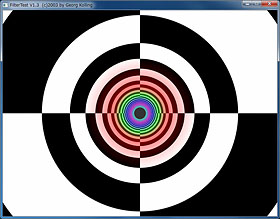

「そもそも,異方性フィルタリングとは何か」という点に関しては,連載バックナンバー「『テクスチャの異方性フィルタリング』ってなに?」を参照してほしいが,まず,このスライドで右に見える画像は,Georg Kolling氏が制作した「Filter Test」によるものだ。

このテストプログラムは,MIPMAPの各縮小レベルを,あえて異なる単色で塗り潰したうえで,画面奥に向かって伸びるトンネルの壁に対して,異方性フィルタリングを適用しながらテクスチャ群をマッピングして(≒貼り付けて)いくというものである。

視点はトンネルの中心にあり,奥にあるもう一方の出口方向を見据えている。そのため,色分けされたMIPMAP階層の切り替わり境界は,滑らかな同心円状を持ってトンネルに現れることが理想となる。HD 5800シリーズのテスト結果は,この理想形そのものになるというのが,上で紹介したスライドなのだ。

参考までに,まさにその手抜きを積極的に行っていた“悪例”として,「Radeon X800 Pro」のテスト結果を右に示しておきたい。

ところで,第2回で示したスライドにも書かれていたのだが,AMDの公式スペック資料だと,HD 5870のテクスチャユニット数は,20基ではなく,80基になっている。

これは,各テクスチャユニットのクロック当たりスループットが,バイリニアフィルタ・テクセル4個分であることに起因するもの。つまり,「バイリニアフィルタ適用済みFP32テクスチャ」のクロック当たりスループットが,テクスチャユニット1基当たり4テクセルなので,全体としては80テクセル(=4テクセル×20基)相当であることを受けた値である。もっというと,競合であるNVIDIAのカウント方式に合わせた,“数字ゲーム”のスコアだ。

ともあれ,HD 5870が持つバイリニアフィルタ適用済みFP32テクスチャのフィルレートは,80テクセル×850MHzで毎秒68億テクセルとなる。

HD 4800シリーズにおいてアーキテクチャが刷新されたとき,「ATI Radeon HD 2000/3000」世代から,キャッシュシステムが大幅に見直されたが,HD 5800シリーズではさらなるキャッシュシステムの改良が施された。

HD 5870を例に書き進めると,L1テクスチャキャッシュからSIMD Engineへの伝送帯域幅――すなわち,SIMD Engineの最大フェッチ速度――は毎秒1TBにまで高められたとのこと。HD 4870の同480GBと比べると,2倍以上だが,これはおそらく,L1キャッシュとSIMD Engineを結ぶバス帯域幅を2倍にしたことで実現されているのだろう。なお,L1テクスチャキャッシュの容量そのものは前世代と同じ8kBだと発表されている。

L2キャッシュは,メモリコントローラ側に実装されているが,これはHD 4800シリーズと同じ設計。HD 4800時代だと,その容量は非公開とされていたのに対し,今回は「HD 5800シリーズのL2キャッシュ容量は,メモリコントローラ1基当たり,前世代比で2倍の128kBとなった」(Demers氏)と公表されている。つまり,HD 4800シリーズだとメモリコントローラ当たり64kBだったわけだ。

なお,L2キャッシュからL1テクスチャキャッシュへの伝送速度は毎秒435GB。HD 5870とHD 4870の間にある,動作クロック分の違いしか性能は向上していないので,バス幅の拡張は行われていないはずである。

ROPユニット(ROP:Rendering Output Pipeline)と呼ばれることもあるRender Back-End(レンダーバックエンド,以下日本語表記)も,基本的なデザインはHD 4800シリーズと同じだ。

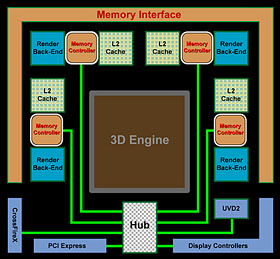

HD 5870のレンダーバックエンド数はHD 4870の16基から倍増を果たした32基と発表されているが,AMDの示したブロックダイアグラムだと,8基しかないように見える。

HD 5870のメモリコントローラとレンダーバックエンド周りをクローズアップしたもの。レンダーバックエンドは,4基のメモリコントローラに2基ずつ実装され,計8基となっている

実はこれも,テクスチャユニット数と同じで,競合とスペックを並べて比較するための数字だ。ATI Radeon HD系のレンダーバックエンドは1クロック当たり2×2の4ピクセル(≒4テクセル)出力が可能となっているので,HD 5870の場合,4ピクセル×8基=32ピクセルで,「32基相当」というわけである。

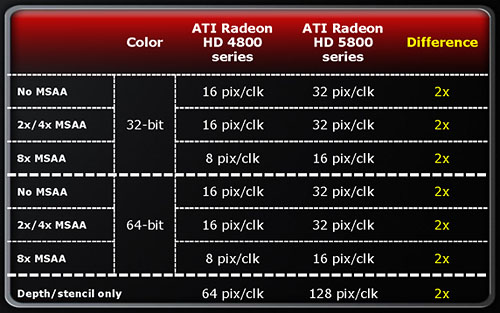

いずれにせよ,下の表を見ると分かるように,スペック的にはHD 4870比で2倍のピクセルスループットを達成できている。

Demers氏によれば,レンダーバックエンドは,従来製品比で“ただ2倍に増えた”のではなく,細かな改良が行われているとのこと。

例えば,HD 4800シリーズでカットされた,高速にバッファをクリアする専用ロジックを,HD 5800シリーズでは復活させたという。これについては「HD 4800シリーズで,一部の3Dゲームなどでパフォーマンス低下が確認されたため」(Demers氏)だそうだ。

もう一つ,圧縮したままのテクスチャデータを内部バスに流し,テクスチャユニット側で展開できる仕組みも,HD 5800の新機能だ。

シーンを別の視点などからテクスチャにレンダリングし,これをテクスチャ素材として最終的なシーンレンダリングに活用するマルチパスレンダリングは,今や当たり前の手法。だが,最近ではシーンだけでなく,物理事象をもGPUでシミュレートし,その結果をデータテーブルとしてテクスチャにレンダリングし,これを最終的なシーンレンダリングに活用する手法も一般化しているため,テクスチャ参照頻度はますます上昇している。

HD 4800シリーズまでは,テクスチャユニットからテクスチャを参照するとき,そのテクスチャが圧縮されている場合,これをレンダーバックエンド側でデコードしてからテクスチャユニットへ伝送していた。ここにHD 5800シリーズではメスが入ったわけである。

俯瞰視点で,テクスチャユニットが取り扱うテクスチャデータそのものを見ると,HD 4800シリーズ以前とHD 5800シリーズとの間には何の違いもない。しかし,レンダーバックエンドとL1テクスチャキャッシュを結ぶ内部バスに流れるデータは圧縮済みのものになるため,帯域幅の消費を抑えられる。

この設計改善は,テクスチャ内アンチエイリアシング処理のパフォーマンス向上にも貢献するはずというのが,AMDの目論みだ。

Multi-Sample Anti-Aliasing(マルチサンプル・アンチエイリアシング,MSAA)では,アンチエイリアス処理解像度,つまりサブピクセル解像度の深度値をキーにしてポリゴンエッジを検出し,アンチエイリアシングを行う。これに対し,Transparency Anti-Aliasing(トランスペアレンシー・アンチエイリアシング,TAA)処理,やCustom Filter Anti-Aliasing(カスタムフィルタ・アンチエイリアシング,CFAA)処理などでは,例えば透明テクセルか,不透明テクセルかといった判断など,テクスチャの内容を吟味してアンチエイリアシングを行う。要するに,テクスチャ参照頻度が増すのだ。

今回の改良によって,そのときのバス消費を低減できるため,結果的にパフォーマンスが向上するはずという読みなのである。なお,TAAについては筆者の連載バックナンバー「ATI,Radeon X1000シリーズ発表でSM3.0世代に突入」を,CFAAについては同じく「ATI Radeon HD 2000シリーズのGPUアーキテクチャ徹底解説」をそれぞれ参照してほしい。

右に示したのは,レンダーバックエンドを説明したときに用いたのと同じ図だが,これを参考に,メモリインタフェースを見ていこう。

メモリコントローラのインタフェースは1基当たり64bit幅(32bit幅×2)。各メモリコントローラにはレンダーバックエンドとL2キャッシュが接続されていて,このブロックが四つあると分かる。メモリインタフェースとしては64bit幅×4基で256bitのメモリインタフェースを有していることになる計算だ。

同じ256bitメモリインタフェースということもあり,構成はHD 4800シリーズとよく似ているが,前述したとおりHD 5800シリーズでは,L2キャッシュ容量が前世代と比べて2倍となる128kBになり,メモリコントローラ1基当たりのレンダーバックエンド数も倍増するという形で拡張が行われている。

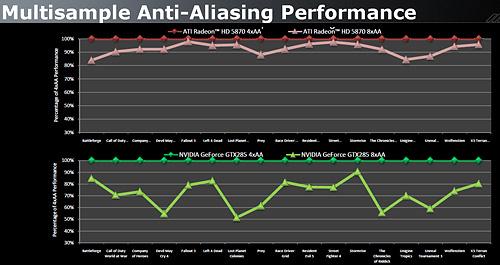

この「レンダーバックエンド数,L2キャッシュ容量ともに前世代比2倍」は,局所Zバッファの反復読み出しと局所カラーバッファへの書き出しを頻発させるMSAA適用時に,パフォーマンスが低下するのを抑制する効果がある。それを示すのが,AMDの示す,以下のデータだ。

このグラフは,4x MSAA適用時のパフォーマンスを100%として,8x MSAA適用時のパフォーマンス低下率を表したものだ。上がHD 5870,下がNVIDIAの「GeForce GTX 285」だが,HD 5870のほうが,8x MSAA適用時のパフォーマンス低下率が大きくないことを見て取れる。

メモリコントローラ関連では,新しく,エラーチェック機構としてEDC(Error Detection Code)機能が組み込まれたのもトピックだ。

EDCは,高クロックのGDDR5メモリを利用することが前提となるHD 5800シリーズで,データの信頼性を向上させる。また,Demers氏は「EDCはグラフィックスメモリのオーバークロック時に,描画不全やクラッシュが発生するのを防ぐのにも一役買うだろう」と予見する。

もちろん,HD 5800シリーズを科学技術計算などのHPC用途(≒GPGPU用途)で使用するときの信頼性を高める意味もあるだろう。

このほか,第1回で紹介したとおり,GDDR5に対し,電圧や動作クロックの動的な制御といった,アグレッシブな省電力制御を行うロジックもメモリコントローラには実装されている。

なお,あらためて断るまでもないかもしれないが,公称27Wの低クロック動作時であっても,2Dのデスクトップを表示するために必要十分なスループットは維持されているとのことだ。

HD 5800シリーズが持つGPGPU的なポテンシャルについても言及しておきたい。

Demers氏は,HD 5800シリーズのGPGPUフィーチャーについて,「『OpenCL 1.0』と,DirectX 11の『DirectCompute(11)』へフォーカスした設計を行った」と強調している。

NVIDIAと異なり,独自のGPGPUプラットフォームを立ち上げるのには事実上失敗したAMD。それを受けて同社は,自らのGPGPUソリューション,「ATI Stream」を,OpenCLとDirectComputeの上でこそ成り立つものと定義し直した。結果,ATI Streamという名称は,AMDのマーケティングキーワードへとその立ち位置を変えつつある。

CUDAの成功は高く評価されるべきだが,競合たるAMDとしてはそれを認めるわけにもいかないため,最近では「3dfxの『Glide』がDirectXで置き換えられたように,CUDAもOpenCLやDirectComputeで置き換えられるはず」という,かなり攻撃的なメッセージでNVIDIAを牽制している。このあたりはたいへん泥臭い話だが,いずれ時間が決着をつけてくれるだろう。

話を戻そう。Demers氏は,「HD 5800シリーズはOpenCL 1.0のオプション機能も含め,すべての要求仕様に対応した。付け加えると,2010年に登場予定となっている次期バージョンのOpenCLにもフル対応を行える(ハードウェア的な)準備がある」とアピールしている。

下は,HD 5870の全体ブロックダイアグラムを,GPGPUに関係する部分にフォーカスした形で作り直したものとして見てほしい。図に見える「Fetch Unit」とはテクスチャユニットのことであり,「8kB L1」はL1テクスチャキャッシュのことだ。「GPGPU目的で活用されるときには,便宜上,呼び名が変わる」という理解でいい。

GPGPU関連部分にフォーカスした,HD 5870の全体ブロックダイアグラム

GPGPUとしてのHD 5800シリーズが持つ演算精度は,IEEE 754-2008に準拠したものとなっている。

IEEE 754-2008は,「浮動小数点演算における誤差の丸め方」を規定したもので,計算時の例外処理事例などを,近代のHPC環境に合わせて規定した規格だ。今世代のGPGPU対応はこのIEEE 754-2008規格というものが大きな基準かつキーワードになっているようで,NVIDIAなども次世代GPUアーキテクチャ「Fermi」(フェルミ)ベースのGPGPU製品ではこれに合わせている。

ちなみに,HD 5800シリーズでは演算精度に関してのみIEEE 754-2008準拠となっており,例外処理時(※例えば計算結果が無限大になるようなケース)の割り込み処理には対応しない。

図をもう少し詳しく見てみると,HD 4800シリーズで「Shader Export Buffer」と呼ばれていたブロックは,HD 5800シリーズでは「Memory Export Buffer」と呼び名が変わり,容量は2倍に増加された。

データ並列コンピューティングでは取り扱うデータが大量なので,その入出力はまとめて行わないと非効率的だ。しかし,演算結果は同じタイミングで一斉に出力されるとは限らない。

Memory Export Bufferは,SIMD Engine群から出力されてくる,言ってみればバラバラの演算結果データを取りまとめてメモリに書き出すための一時バッファなのだ。1クロックで32bitデータを64個出力するポテンシャルがある。

各SIMD Engine内のThread Processor(=5SP)からの出力結果をほかのThread Processorと共有するためのローカルメモリ「Local Data Share」は,SIMD Engine当たり32kBと,HD 4800シリーズのときから2倍化。すべてのSIMD Engineをまたいで共有される,データの一時格納用ローカルメモリ「Global Data Share」は64kBとなった。これは, HD 4800シリーズの16kBから4倍の大増量だ。

これらLocal&Global Data ShareはGPGPU用途でこそ活用されるものであり,そこが強化されているのは,AMDのGPGPUに賭ける本気度を表しているといえよう。

3Dグラフィックス面では「DirectX 11へのフル対応」,GPGPU面では「OpenCL 1.0とDirectComputeへのフル対応」というテーマに取り組んだHD 5800シリーズだが,基本アーキテクチャはあくまでもHD 4800シリーズのリファインといえる。

製造プロセスのシュリンクがあったことで,細かな改良を行ったり,シェーダコアであるSIMD Engineを強化する余裕が生まれたというイメージだ。大ざっぱに,「シェーダ(≒SIMD Engine)を2倍にして,DirectX 11に対応させたHD 4800」と捉えても,間違いではない。

特徴的なのは,AMDは今回もVLIW(Very Long Instruction Word)命令ベースのスーパースカラアーキテクチャを死守してきたところ。AMDとしては,「GPUが行うべき最優先の仕事は3Dグラフィックスであり,その処理に適しているアーキテクチャは5基のSPをひとまとめにしたスーパースカラ構成である。だから,今回もこれを踏襲した」という設計思想なのだ。

今回は,依存関係のある命令を1クロック内で実行することを可能にする斬新な改良までが施され,スーパースカラ構成のメリットがさらに生きることとなった。

命令粒度やスレッド粒度が必然的に細かく,しかもランダム性が強まるGPGPU用途では,VLIWのメリットが生きにくくなる可能性が高いが,この弱点を少しでも隠蔽できるようにと,HD 5800シリーズで採用されたのが,キャッシュシステムの洗練や,内部バスの高速化などといった,データパスの高速化だ。この工夫が実際にどのようなパフォーマンスを見せてくれるのか,興味深い。

OpenCL 1.0とDirectComputeの本格普及後は,ATI RadeonとGeForceで同一のGPGPUアプリケーションを動かせるようになるわけなので,このときのパフォーマンスがどう変わってくるかは注目しておきたいところだ。

そんなHD 5800シリーズのアーキテクチャで,あえて気になる点を挙げるとすれば,それは,レンダーバックエンドが先代の2倍となる32基相当になったにもかかわらず,グラフィックスメモリバス幅が拡張されておらず,メモリクロックも33%しか引き上げられていない点だろうか。

おそらくこの,レンダーバックエンドがオーバーキルだというのは,「より高速なGDDR5メモリが登場してきたときのために,将来へのヘッドルームを残した」ということなのだろう。

HD 4800シリーズの解説記事でも少し触れたが,GDDR5は将来的に,1.5GHz駆動,データレート6Gbpsへ到達する予定だ。仮にこのメモリと組み合わせられれば,HD 5800シリーズのメモリバス帯域幅は毎秒192GBにまで高まる。

時間の経過に合わせてになるか,競合の動きに反応してになるかは分からないが,将来的にはこの,より高速なGDDR5メモリを組み合わせたカードが投入されるはず。32基のレンダーバックエンドが真価を発揮するのは,このタイミングになるはずだ。

- 関連タイトル:

ATI Radeon HD 5800

ATI Radeon HD 5800

- この記事のURL:

(C)2009 Advanced Micro Devices, Inc.