ニュース

Intelが発表した「3次元トライゲート・トランジスタ」って何だ? 「Ivy Bridgeの性能を大きく引き上げる技術」の正体に迫る

|

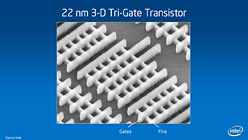

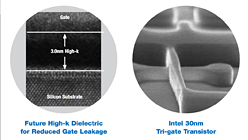

3次元トライゲート・トランジスタは,2002年の時点でIntel Researchが研究開発成果を公表していたもの。簡単にいうと,電流を制御するゲートの構造を従来の2次元から3次元へ移行させることで,漏れ電流を抑制するとともに,トランジスタの密度を向上させる技術である。

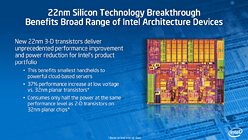

3次元トライゲート・トランジスタの採用で

低消費電力時に従来比最大37%の性能向上を実現

「なんかすごそうだけど,どういうこと?」と思った4Gamer読者は多いだろう。まず最初に,トランジスタとはどんなものなのかを説明しておきたい。

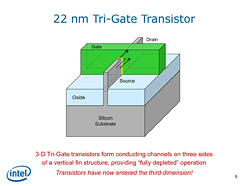

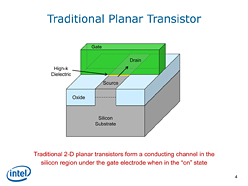

一般的なトランジスタは,「ソース」(Source)と呼ばれる電流の貯蔵エリアと,「ドレイン」(Drain)と呼ばれる排出路,ソースとドレインの間で電流の流れを制御する「ゲート」(Gate)の3つで構成されている。ソースとドレインの間にゲート(≒堰)を設けることで,電流を流したり流さなかったりという制御を行っているわけだ。

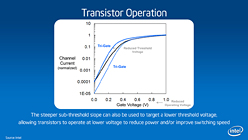

Pentium 4の頃,半導体プロセス技術の進歩により,ゲートそのものが微細化し,結果として漏れ電流(リーク,Leakage)が急増。消費電力や熱量が飛躍的に増大してしまったということを憶えている読者も多いことだろう。

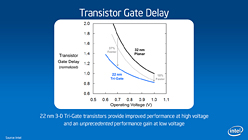

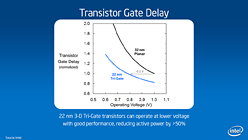

そこで,今日(こんにち)的なメインストリーム向けのCPUやGPUでは,ゲートの長さを大きくとることで,漏れ電流の増大を防いでいる。ただ,これにはトレードオフがあり,チップ上に搭載できるトランジスタの数を増やす「トランジスタの高密度化」の妨げになっているほか,ソースからドレインへと電流が流れるときの遅延時間が大きくなることが,動作クロックの引き上げを難しくする要因にもなってしまっているのだ。

|

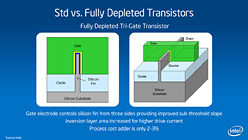

3次元トライゲート・トランジスタでは,ソースとドレインを“台地”としてシリコン基質上に構築し,その間に,“厚みのある壁”としてのゲートを設置することで,ソースとドレインを立体的に塞ぐ。そして,従来は1面だけで電流制御していたところ,左右と上の3面で電流制御をできるようにすることにより,漏れ電流を抑制する。ゲートが3面に亘(わた)るからトライゲート(Tri-Gate)というわけだ。

現地時間5月4日の発表会で登壇したIntelのMark Bohr(マーク・ボア)シニアフェローは,「この構造ではソースとドレインの面積も増やせるため,より多くの電流をトランジスタへ流せる。また,ゲート長も短くできるため,高クロック化などの高性能化も容易になる」とも説明していた。

|

|

|

さらに,リーク電流は10分の1に抑えられるようになるほか,「ゲート長を短くできるので,トランジスタ密度を2倍に引き上げることが可能となる。そのため,ウェハの製造コストは従来比で2〜3%増に留まり,コスト面での影響がほとんどない」(Bohr氏)のも大きなメリットとされる。

|

今回,3次元トライゲート・トランジスタが量産可能な技術になったことで,「現在,CPUの多くを占めているSRAM(キャッシュ)領域の密度を高められるようになる」とBohr氏。つまり,より小さなダイ面積に大容量のキャッシュを搭載できる可能性があるわけだ。

そんな3次元トライゲート・トランジスタ採用の第1弾製品となるIvy Bridgeだが,試作ウェハはすで完成しており,今回の発表にあわせてクライアント向けのIvy Bridgeと,2コアのサーバー向けIvy Bridgeでデモが披露されている。

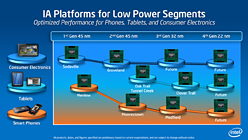

なお,Intelは,Atomプロセッサにも3次元トライゲート・トランジスタを採用する計画があるとのこと。製造プロセス技術で優位に立つことにより,スマートフォンを含む低電圧デバイス分野でも大幅な性能向上と市場シェア拡大を狙っているようだ。

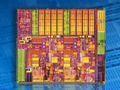

Ivy Bridgeで22nmプロセス技術を採用する3次元トライゲート・トランジスタを採用。性能向上と省電力性能の向上を果たす |

Atomプロセッサも22nmプロセス技術を採用する3次元トライゲート・トランジスタへと順次移行していく |

トライゲートでムーアの法則を維持

2013年には14nmプロセス技術を採用へ

|

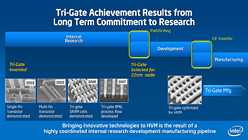

2002年以降,Intelは3次元トライゲート・トランジスタの研究と開発の成果を繰り返し公表してきている。実際,2005年には,30nmプロセス技術を採用した3次元トライゲート・トランジスタの試作も行われていた。

Bohr氏は,今回の意義について,「競合他社も1Xnmプロセス世代で採用することを表明している。立体構造のトランジスタそのものは目新しい技術ではない」としつつも,「22nmプロセス技術での量産を実現したことで,我々は2〜3年のアドバンテージを得たことになる」と胸を張る。

Intelは2002年から,3Dトライゲート・トランジスタ技術の量産化を目指し,研究と開発を続けている |

2005年にIntel Researchが公表した,30nmプロセス世代における3次元トライゲート・トランジスタの試作品 |

|

というのも,2008年の時点でIntelは,22nmプロセスの次を16nmプロセスと位置づけていたのに対し,2010年になるとこれが15nmプロセス,そして今回の発表では14nmプロセスと,進化の速度を大幅に進めているからである。トランジスタの集積度に大きな影響を与える3次元トライゲート・トランジスタ技術を22nmプロセス世代で確立できたことが大きな要因と見るべきだろう。

一方で,この2年の間にIntelがプロセス計画を大幅に変更した背景には,現在半導体の製造に用いられているDUV(Deep Ultra-Violet,深紫外線)リソグラフィよりも微細な回路を実現できる,次世代露光技術EUV(Extreme Ultra-Violet,極端紫外)を採用できる目処が立ったからと見ている半導体業界関係者もいるようである。

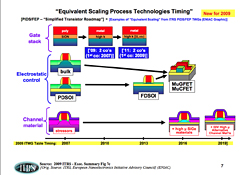

3次元トライゲート・トランジスタに至る道程。2007年のHigh-kメタルゲート以来となる重要な技術革新と位置づけられる |

こちらは「Intel Developer Forum 2008 San Francisco」の基調講演で公開されたもの。22nmプロセスの次は16nmだ |

2010年の投資家向け会議で公開されたプロセスロードマップ。ここだと,22nmプロセスの次は15nmプロセスになっている |

|

これは,Sandy Bridgeのシュリンク版という位置づけになるIvy Bridgeでも,3次元トライゲート・トランジスタ技術の採用により,消費電力を低減させつつ,より高クロックな製品が投入しやすい状況になったことを意味する。実際,Ivy Bridgeのデモを披露したDavid(Dadi) Perlmutter(ダディ・ パルムッター)上級副社長は,試作シリコンの段階でもIvy Bridgeが良好なパフォーマンスを発揮しているとアピールしていた。

今回,3次元トライゲート・トランジスタ技術の量産化が可能になったことは,Intelは,単に「半導体の集積度を引き上げられるようになった」だけではなく,CPUの高性能化ペースを再び上げていく体制が整ったともいえそうだ。

- 関連タイトル:

Core i7・i5・i3-3000番台(Ivy Bridge)

Core i7・i5・i3-3000番台(Ivy Bridge) - この記事のURL: